Hello,

I’m working on a project to make the LimeSDR-XTRX a frequency translator.The final product will not have access to python/GNU Radio, so I’m taking the route of updating the firmware by trying to loop the Rx data from the RFIC into the Tx data path of the RFIC. I figure that way I can still use the LimeSuiteNG gui to control the Tx and Rx frequencies.

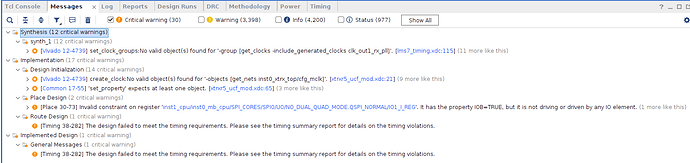

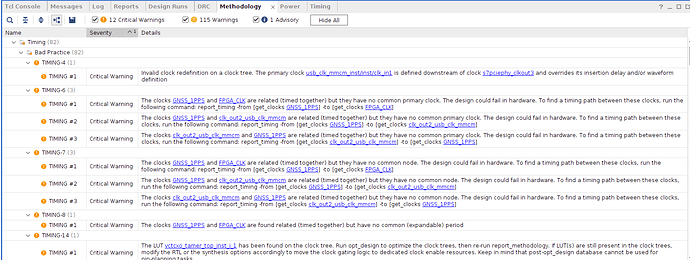

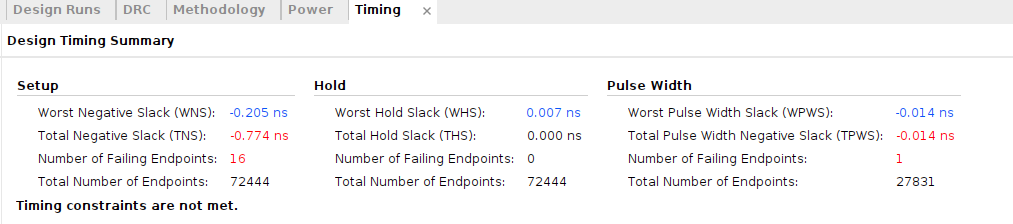

I’ve downloaded the repo and have run the “Generate_Project.tcl” file. Using Vivado 2022.1, I tried generating the bitstream and I failed timing. I want to make sure my base project is correct before I start tinkering with things. Has anyone else had this issue when trying to generate the bit file from Vivado? Below are some screenshots of various reports, I tried to attach them as text files but wasn’t able to.

I did come across this post, LimeSDR-USB Quartus 15.1 fails timing, but it for Quartus, a different device, and 4 years old.

Thank you,

Joe