I think I have similar problem.

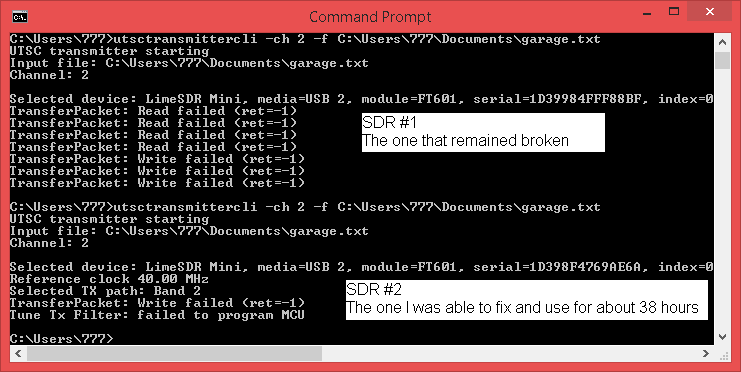

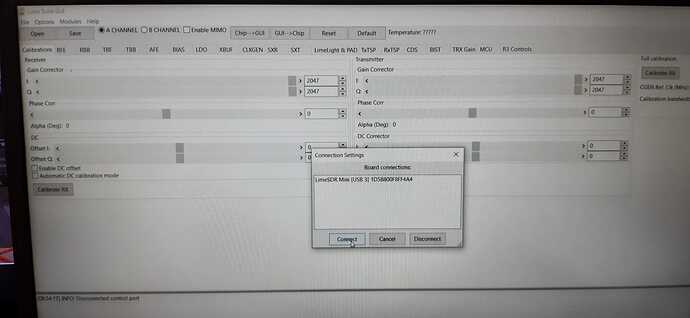

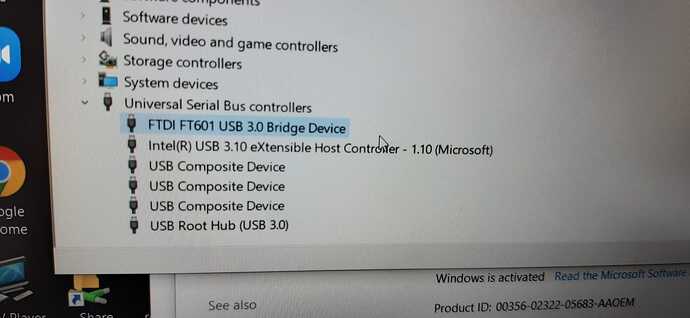

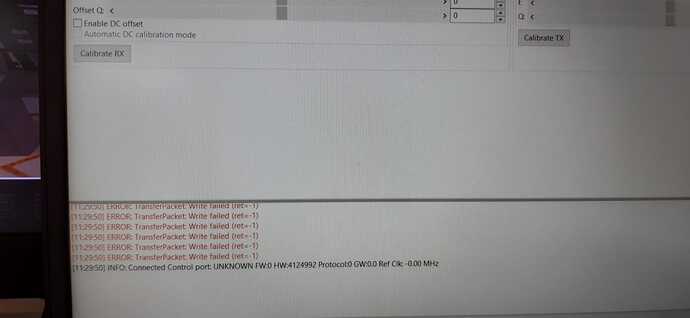

Using LimeSDR mini

PS C:\Program Files\PothosSDR\bin> .\LimeQuickTest.exe

[ TESTING STARTED ]

->Start time: Tue Nov 23 16:47:47 2021

->LimeSuite version: 20.10.0-PothosSDR-2021.07.25-vc16-x64

TransferPacket: Write failed (ret=-1)

TransferPacket: Write failed (ret=-1)

TransferPacket: Write failed (ret=-1)

TransferPacket: Write failed (ret=-1)

TransferPacket: Write failed (ret=-1)

TransferPacket: Write failed (ret=-1)

Board not supported

Failed to connect

PS C:\Program Files\PothosSDR\bin> .\limeutil --info

######################################################

LimeSuite information summary

######################################################

Version information:

Library version: v20.10.0-PothosSDR-2021.07.25-vc16-x64

Build timestamp: 2021-07-25

Interface version: v2020.10.0

Binary interface: 20.10-1

System resources:

Installation root: C:\Program Files\PothosSDR

User home directory:

App data directory: C:\Users\ct_lee\AppData\Roaming/LimeSuite

Config directory: /.limesuite

Image search paths:

- C:\Users\ct_lee\AppData\Roaming/LimeSuite/images

- C:\Program Files\PothosSDR/share/LimeSuite/images

Supported connections:

PS C:\Program Files\PothosSDR\bin> .\SoapySDRUtil --probe=“driver=lime”

######################################################

Soapy SDR – the SDR abstraction library

######################################################

Probe device driver=lime

←[1m←[33m[WARNING] SoapyVOLKConverters: no VOLK config file found. Run volk_profile for best performance.←[0m

[INFO] Make connection: ‘LimeSDR Mini [USB 3] 1D4C2AF75EB323’

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

[INFO] Device name: UNKNOWN

[INFO] Reference: -1e-06 MHz

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

[INFO] LMS7002M register cache: Disabled

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] SetFrequencyCGEN(61.44 MHz) failed←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

…

– Device identification

driver=FT601

hardware=UNKNOWN

boardSerialNumber=0xf75eb323

expansionName=UNKNOWN

firmwareVersion=0

gatewareVersion=0.0

hardwareVersion=0

protocolVersion=0

– Peripheral summary

Channels: 2 Rx, 2 Tx

Timestamps: YES

Sensors: clock_locked, lms7_temp

* clock_locked (Clock Locked): false

CGEN clock is locked, good VCO selection.

* lms7_temp (LMS7 Temperature): 0.000000 C

The temperature of the LMS7002M in degrees C.

Registers: BBIC, RFIC0

Other Settings:

* SAVE_CONFIG - Save LMS settings to file

[key=SAVE_CONFIG, type=string]

* LOAD_CONFIG - Load LMS settings from file

[key=LOAD_CONFIG, type=string]

* OVERSAMPLING - oversampling ratio (0 - auto)

[key=OVERSAMPLING, type=int, options=(0, 1, 2, 4, 8, 16, 32)]

GPIOs: MAIN

– RX Channel 0

Full-duplex: YES

Supports AGC: NO

Stream formats: CF32, CS12, CS16

Native format: CS16 [full-scale=32767]

Stream args:

* Buffer Length - The buffer transfer size over the link.

[key=bufferLength, units=samples, default=0, type=int]

* Link Format - The format of the samples over the link.

[key=linkFormat, default=CS16, type=string, options=(CS16, CS12)]

* Skip Calibration - Skip automatic activation calibration.

[key=skipCal, default=false, type=bool]

* align phase - Attempt to align phase of Rx channels.

[key=alignPhase, default=false, type=bool]

Antennas: NONE, LNAH, LNAL, LNAW, LB1, LB2

Corrections: DC removal, DC offset, IQ balance

Full gain range: [-12, 61] dB

TIA gain range: [0, 12] dB

LNA gain range: [0, 30] dB

PGA gain range: [-12, 19] dB

Full freq range: [0, 3800] MHz

RF freq range: [30, 3800] MHz

BB freq range: [6.25e-08, -6.25e-08] MHz

Tune args:

* LO Offset - Tune the LO with an offset and compensate with the baseband CORDIC.

[key=OFFSET, units=Hz, default=0.0, type=float]

* BB - Specify a specific value for this component or IGNORE to skip tuning it.

[key=BB, units=Hz, default=DEFAULT, type=float, options=(DEFAULT, IGNORE)]

Sample rates: [0.1, 61.44] MSps

Filter bandwidths: [1.4001, 130] MHz

Sensors: lo_locked

* lo_locked (LO Locked): false

LO synthesizer is locked, good VCO selection.

Other Settings:

* TSP_CONST - Digital DC test signal level in LMS7002M TSP chain.

[key=TSP_CONST, default=16383, type=int, range=[0, 32767]]

* CALIBRATE - DC/IQ calibration bandwidth

[key=CALIBRATE, type=float, range=[2.5e+06, 1.2e+08]]

* ENABLE_GFIR_LPF - LPF bandwidth (must be set after sample rate)

[key=ENABLE_GFIR_LPF, type=float]

* TSG_NCO - Enable NCO test signal

[key=TSG_NCO, default=4, type=int, options=(-1, 4, 8)]

– RX Channel 1

Full-duplex: YES

Supports AGC: NO

Stream formats: CF32, CS12, CS16

Native format: CS16 [full-scale=32767]

Stream args:

* Buffer Length - The buffer transfer size over the link.

[key=bufferLength, units=samples, default=0, type=int]

* Link Format - The format of the samples over the link.

[key=linkFormat, default=CS16, type=string, options=(CS16, CS12)]

* Skip Calibration - Skip automatic activation calibration.

[key=skipCal, default=false, type=bool]

* align phase - Attempt to align phase of Rx channels.

[key=alignPhase, default=false, type=bool]

Antennas: NONE, LNAH, LNAL, LNAW, LB1, LB2

Corrections: DC removal, DC offset, IQ balance

Full gain range: [-12, 61] dB

TIA gain range: [0, 12] dB

LNA gain range: [0, 30] dB

PGA gain range: [-12, 19] dB

Full freq range: [0, 3800] MHz

RF freq range: [30, 3800] MHz

BB freq range: [6.25e-08, -6.25e-08] MHz

Tune args:

* LO Offset - Tune the LO with an offset and compensate with the baseband CORDIC.

[key=OFFSET, units=Hz, default=0.0, type=float]

* BB - Specify a specific value for this component or IGNORE to skip tuning it.

[key=BB, units=Hz, default=DEFAULT, type=float, options=(DEFAULT, IGNORE)]

Sample rates: [0.1, 61.44] MSps

Filter bandwidths: [1.4001, 130] MHz

Sensors: lo_locked

* lo_locked (LO Locked): false

LO synthesizer is locked, good VCO selection.

Other Settings:

* TSP_CONST - Digital DC test signal level in LMS7002M TSP chain.

[key=TSP_CONST, default=16383, type=int, range=[0, 32767]]

* CALIBRATE - DC/IQ calibration bandwidth

[key=CALIBRATE, type=float, range=[2.5e+06, 1.2e+08]]

* ENABLE_GFIR_LPF - LPF bandwidth (must be set after sample rate)

[key=ENABLE_GFIR_LPF, type=float]

* TSG_NCO - Enable NCO test signal

[key=TSG_NCO, default=4, type=int, options=(-1, 4, 8)]

– TX Channel 0

Full-duplex: YES

Supports AGC: NO

Stream formats: CF32, CS12, CS16

Native format: CS16 [full-scale=32767]

Stream args:

* Buffer Length - The buffer transfer size over the link.

[key=bufferLength, units=samples, default=0, type=int]

* Link Format - The format of the samples over the link.

[key=linkFormat, default=CS16, type=string, options=(CS16, CS12)]

* Skip Calibration - Skip automatic activation calibration.

[key=skipCal, default=false, type=bool]

* align phase - Attempt to align phase of Rx channels.

[key=alignPhase, default=false, type=bool]

Antennas: NONE, BAND1, BAND2

Corrections: DC offset, IQ balance

Full gain range: [-12, 64] dB

PAD gain range: [0, 52] dB

IAMP gain range: [-12, 12] dB

Full freq range: [0, 3800] MHz

RF freq range: [30, 3800] MHz

BB freq range: [2.5e-07, -2.5e-07] MHz

Tune args:

* LO Offset - Tune the LO with an offset and compensate with the baseband CORDIC.

[key=OFFSET, units=Hz, default=0.0, type=float]

* BB - Specify a specific value for this component or IGNORE to skip tuning it.

[key=BB, units=Hz, default=DEFAULT, type=float, options=(DEFAULT, IGNORE)]

Sample rates: [0.1, 61.44] MSps

Filter bandwidths: [5, 40], [50, 130] MHz

Sensors: lo_locked

* lo_locked (LO Locked): false

LO synthesizer is locked, good VCO selection.

Other Settings:

* TSP_CONST - Digital DC test signal level in LMS7002M TSP chain.

[key=TSP_CONST, default=16383, type=int, range=[0, 32767]]

* CALIBRATE - DC/IQ calibration bandwidth

[key=CALIBRATE, type=float, range=[2.5e+06, 1.2e+08]]

* ENABLE_GFIR_LPF - LPF bandwidth (must be set after sample rate)

[key=ENABLE_GFIR_LPF, type=float]

* TSG_NCO - Enable NCO test signal

[key=TSG_NCO, default=4, type=int, options=(-1, 4, 8)]

– TX Channel 1

Full-duplex: YES

Supports AGC: NO

Stream formats: CF32, CS12, CS16

Native format: CS16 [full-scale=32767]

Stream args:

* Buffer Length - The buffer transfer size over the link.

[key=bufferLength, units=samples, default=0, type=int]

* Link Format - The format of the samples over the link.

[key=linkFormat, default=CS16, type=string, options=(CS16, CS12)]

* Skip Calibration - Skip automatic activation calibration.

[key=skipCal, default=false, type=bool]

* align phase - Attempt to align phase of Rx channels.

[key=alignPhase, default=false, type=bool]

Antennas: NONE, BAND1, BAND2

Corrections: DC offset, IQ balance

Full gain range: [-12, 64] dB

PAD gain range: [0, 52] dB

IAMP gain range: [-12, 12] dB

Full freq range: [0, 3800] MHz

RF freq range: [30, 3800] MHz

BB freq range: [2.5e-07, -2.5e-07] MHz

Tune args:

* LO Offset - Tune the LO with an offset and compensate with the baseband CORDIC.

[key=OFFSET, units=Hz, default=0.0, type=float]

* BB - Specify a specific value for this component or IGNORE to skip tuning it.

[key=BB, units=Hz, default=DEFAULT, type=float, options=(DEFAULT, IGNORE)]

Sample rates: [0.1, 61.44] MSps

Filter bandwidths: [5, 40], [50, 130] MHz

Sensors: lo_locked

* lo_locked (LO Locked): false

LO synthesizer is locked, good VCO selection.

Other Settings:

* TSP_CONST - Digital DC test signal level in LMS7002M TSP chain.

[key=TSP_CONST, default=16383, type=int, range=[0, 32767]]

* CALIBRATE - DC/IQ calibration bandwidth

[key=CALIBRATE, type=float, range=[2.5e+06, 1.2e+08]]

* ENABLE_GFIR_LPF - LPF bandwidth (must be set after sample rate)

[key=ENABLE_GFIR_LPF, type=float]

* TSG_NCO - Enable NCO test signal

[key=TSG_NCO, default=4, type=int, options=(-1, 4, 8)]

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

←[1m←[31m[ERROR] TransferPacket: Write failed (ret=-1)←[0m

…