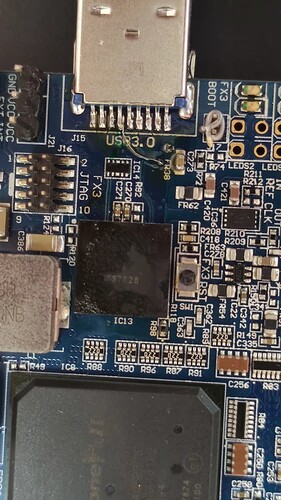

i try replace new CYUSB3014-BZXC,not fix this;

Is there any good suggestion for my next step?

thk

QuickTest Log:

replace before(LimeSDR-Mini_0009081C05C42430.log)

[ TESTING STARTED ]

->Start time: Wed Aug 2 17:37:38 2023

->LimeSuite version: 20.10.0-g1480bfea

->Device: LimeSDR-USB, media=USB 2.0, module=FX3, serial=0009081C05C42430, index=0, HW=4, GW=2.23

Warning: USB3 not available

Serial Number: 0009081C05C42430

Chip temperature: 39 C

[ Clock Network Test ]

->FX3 GPIF clock test

Test results: 37435; 41191; 44947 - PASSED

->Si5351C test

CLK0: 17554 / 17554 - PASSED

CLK1: 17554 / 17554 - PASSED

CLK2: 17554 / 17554 - PASSED

CLK3: 17554 / 17554 - PASSED

CLK4: 17554 / 17554 - PASSED

CLK5: 17554 / 17554 - PASSED

CLK6: 17554 / 17554 - PASSED

->ADF4002 Test

Result: 10 - PASSED

->VCTCXO test

Results : 5112947 (min); 5113083 (max) - PASSED

->Clock Network Test PASSED

[ FPGA EEPROM Test ]

->Read EEPROM

->Read data: 01 00 00 1A B4 01 D5

->FPGA EEPROM Test FAILED

[ LMS7002M Test ]

->Perform Registers Test

->External Reset line test

Reg 0x20: Write value 0xFFFD, Read value 0xFFFD

Reg 0x20: value after reset 0x0FFFF

->LMS7002M Test PASSED

[ RF Loopback Test ]

Note: The test should be run without anything connected to RF ports

->Configure LMS

->Run Tests (TX_2-> LNA_L):

CH0 (SXR=800.0MHz, SXT=805.0MHz): Result:(-14.2 dBFS, 5.00 MHz) - PASSED

CH1 (SXR=800.0MHz, SXT=805.0MHz): Result:(-16.9 dBFS, 5.00 MHz) - PASSED

->Run Tests (TX_1 -> LNA_W):

CH0 (SXR=1800.0MHz, SXT=1805.0MHz): Result:(-16.2 dBFS, 5.00 MHz) - PASSED

CH1 (SXR=1800.0MHz, SXT=1805.0MHz): Result:(-19.6 dBFS, 5.00 MHz) - PASSED

->Run Tests (TX_2-> LNA_H):

CH0 (SXR=2500.0MHz, SXT=2505.0MHz): Result:(-15.7 dBFS, 5.00 MHz) - PASSED

CH1 (SXR=2500.0MHz, SXT=2505.0MHz): Result:(-14.5 dBFS, 5.00 MHz) - PASSED

->RF Loopback Test PASSED

=> Board tests FAILED <=

Elapsed time: 8.36 seconds

replace after(programming )

LimeSDR-Mini_0009061F01151B30.log

[ TESTING STARTED ]

->Start time: Wed Aug 2 18:03:02 2023

->LimeSuite version: 20.10.0-g1480bfea

->Device: LimeSDR-USB, media=USB 2.0, module=FX3, serial=0009061F01151B30, index=0, HW=4, GW=2.23

Warning: USB3 not available

Serial Number: 0009061F01151B30

Chip temperature: 39 C

[ Clock Network Test ]

->FX3 GPIF clock test

Test results: 28731; 32487; 36243 - PASSED

->Si5351C test

CLK0: 17555 / 17554 - PASSED

CLK1: 17555 / 17554 - PASSED

CLK2: 17555 / 17554 - PASSED

CLK3: 17555 / 17554 - PASSED

CLK4: 17555 / 17554 - PASSED

CLK5: 17555 / 17554 - PASSED

CLK6: 17555 / 17554 - PASSED

->ADF4002 Test

Result: 10 - PASSED

->VCTCXO test

Results : 5112946 (min); 5113082 (max) - PASSED

->Clock Network Test PASSED

[ FPGA EEPROM Test ]

->Read EEPROM

->Read data: 01 00 00 1A B4 01 D5

->FPGA EEPROM Test FAILED

[ LMS7002M Test ]

->Perform Registers Test

->External Reset line test

Reg 0x20: Write value 0xFFFD, Read value 0xFFFD

Reg 0x20: value after reset 0x0FFFF

->LMS7002M Test PASSED

[ RF Loopback Test ]

Note: The test should be run without anything connected to RF ports

->Configure LMS

->Run Tests (TX_2-> LNA_L):

CH0 (SXR=800.0MHz, SXT=805.0MHz): Result:(-13.8 dBFS, 5.00 MHz) - PASSED

CH1 (SXR=800.0MHz, SXT=805.0MHz): Result:(-17.0 dBFS, 5.00 MHz) - PASSED

->Run Tests (TX_1 -> LNA_W):

CH0 (SXR=1800.0MHz, SXT=1805.0MHz): Result:(-16.4 dBFS, 5.00 MHz) - PASSED

CH1 (SXR=1800.0MHz, SXT=1805.0MHz): Result:(-18.6 dBFS, 5.00 MHz) - PASSED

->Run Tests (TX_2-> LNA_H):

CH0 (SXR=2500.0MHz, SXT=2505.0MHz): Result:(-14.9 dBFS, 5.00 MHz) - PASSED

CH1 (SXR=2500.0MHz, SXT=2505.0MHz): Result:(-15.2 dBFS, 5.00 MHz) - PASSED

->RF Loopback Test PASSED

=> Board tests FAILED <=

Elapsed time: 9.05 seconds

[ TESTING STARTED ]

->Start time: Wed Aug 2 18:14:28 2023

->LimeSuite version: 20.10.0-g1480bfea

->Device: LimeSDR-USB, media=USB 2.0, module=FX3, serial=0009061F01151B30, index=0, HW=4, GW=2.23

Warning: USB3 not available

Serial Number: 0009061F01151B30

Chip temperature: 52 C

[ Clock Network Test ]

->FX3 GPIF clock test

Test results: 22587; 26343; 30099 - PASSED

->Si5351C test

CLK0: 17554 / 17554 - PASSED

CLK1: 17554 / 17554 - PASSED

CLK2: 17554 / 17554 - PASSED

CLK3: 17554 / 17554 - PASSED

CLK4: 17554 / 17554 - PASSED

CLK5: 17554 / 17554 - PASSED

CLK6: 17554 / 17554 - PASSED

->ADF4002 Test

Result: 10 - PASSED

->VCTCXO test

Results : 5112944 (min); 5113080 (max) - PASSED

->Clock Network Test PASSED

[ FPGA EEPROM Test ]

->Read EEPROM

->Read data: 01 00 00 1A B4 01 D5

->FPGA EEPROM Test FAILED

[ LMS7002M Test ]

->Perform Registers Test

->External Reset line test

Reg 0x20: Write value 0xFFFD, Read value 0xFFFD

Reg 0x20: value after reset 0x0FFFF

->LMS7002M Test PASSED

[ RF Loopback Test ]

Note: The test should be run without anything connected to RF ports

->Configure LMS

->Run Tests (TX_2-> LNA_L):

CH0 (SXR=800.0MHz, SXT=805.0MHz): Result:(-15.0 dBFS, 5.00 MHz) - PASSED

CH1 (SXR=800.0MHz, SXT=805.0MHz): Result:(-18.1 dBFS, 5.00 MHz) - PASSED

->Run Tests (TX_1 -> LNA_W):

CH0 (SXR=1800.0MHz, SXT=1805.0MHz): Result:(-17.6 dBFS, 5.00 MHz) - PASSED

CH1 (SXR=1800.0MHz, SXT=1805.0MHz): Result:(-20.0 dBFS, 5.00 MHz) - PASSED

->Run Tests (TX_2-> LNA_H):

CH0 (SXR=2500.0MHz, SXT=2505.0MHz): Result:(-16.4 dBFS, 5.00 MHz) - PASSED

CH1 (SXR=2500.0MHz, SXT=2505.0MHz): Result:(-16.1 dBFS, 5.00 MHz) - PASSED

->RF Loopback Test PASSED

=> Board tests FAILED <=

Elapsed time: 8.80 seconds