Hello,

I am trying to update LimeSDR-PCIe FPGA GW via JTAG. I have USB blaster from terasic. I am following the guide at this link https://github.com/myriadrf/LimeSDR-PCIe_GW/blob/master/doc/LimeSDR-PCIe_user_guide_V01r00.pdf

I have cloned the GW from

I compiled the code and generated the .jic file after placing the Xillybus files in relevant folders.

The programming stucks at 21% with an error message " Flash loader IP not loaded on device 1"

I am using Quartus Prime 15.1.2 Build 193 Lite edition on Windows 10 host system.

Can anyone help me with this issue. Thanks

Hi,

most likely you did not marked both check-boxes near “Program/configure” after adding .jic file.

- Did you applied settings as shown in Figure 10 in mentioned user guide?

- Have you tried “Auto detect” in programmer to check JTAG chain?

- Have you tried programming .sof file?

- Post a screenshot of your Quartus programmer window with attached .jic

Hi @VytautasB,

1.Yes

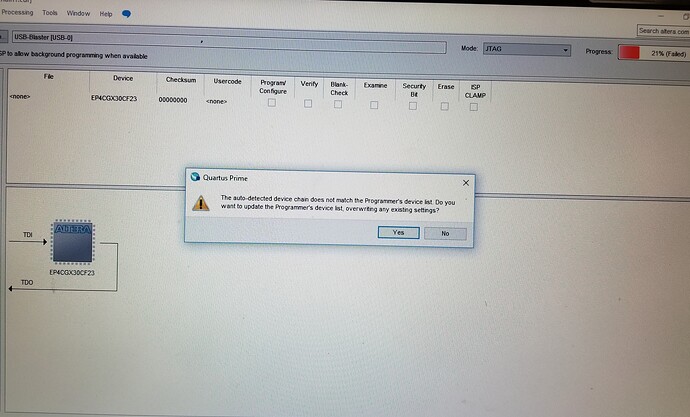

2. Yes, I get the following message

-

Yes that was successful. But I think I have to flash it every time I power cycle the board.

-

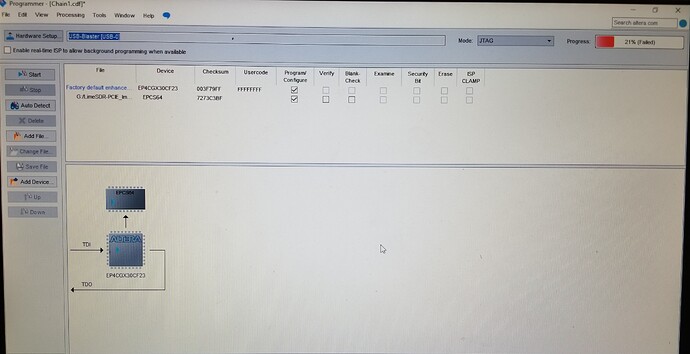

Here

Failure Message

- All the FPGA LEDs are ON, does this indicate something? Also after flashing the .sof file the indication LEDs are solid RED.

-

Yes v1.3

-

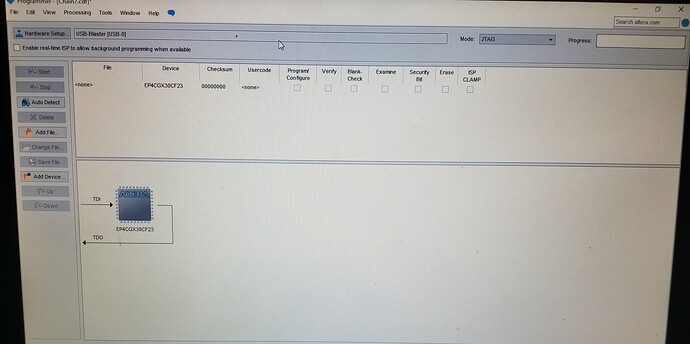

The following is displayed after clicking on Auto Detect

-

I see solid RED Leds only after flashing the .sof file.

First I tried to flash using LimeGUI the process got interrupted in between and the board is like that solid RED LEDs and does not show up in lspci. I thought to flash using JTAG to solve it. But I get this Flash loader issue when using .jic file. I cloned the GW repo and simply compiled it with no changes at all, except that I generated the xillybus ip core files.

Any idea what else can be done to bring up this board?

@Zack @andrewback Any idea what could be wrong here?

If you get solid RED light on both LED and if you did not applied any mods for the board this indicates that .sof file is programmed incorrectly or there are some problem with the board itself.

- Have you tested your Terrasic programming cable with other devices?

- Please use board directly inserted into PCIe slot, do not use any PCIe extension cables.

- Can you try this.sof programming file, just to make sure that we have correct one? This file is compiled and tested on LimeSDR-PCIe v1.3 board from Github master branch, there will be no Xilybus core and no PCIe connection but you should see blinking RED/GREEN light on one of the two LED fitted on the edge of the board.

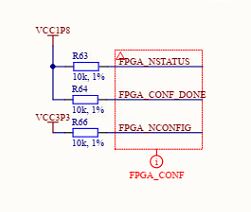

- You could monitor FPGA configuration status pins before/during/after JTAG configuration if you have oscilloscope and post result for me. You can probe them on R63, R64, R66 resistors.

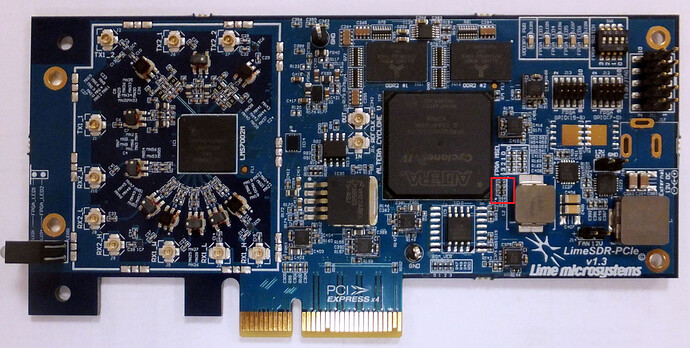

Here you can find mentioned resistors

And schematic fragment