Hi!

We are building a board around LMS7002m IC. As a base for a driver, I’ve chosen LMS7002M-driver.

The system started nicely one or two times, I’ve seen image on a spectrum analyzer. But now it always fails on SXT frequency settings. This log from the last run:

Create LMS7002M instance

rev 0x1

ver 0x7

[INFO] CGEN tune 10.000000 MHz (fref=38.400000 MHz) begin

[TRACE] Trying: fdiv = 202, Ndiv = 52.604167, fvco = 2020.000000 MHz

[DEBUG] Using: fdiv = 202, Ndiv = 52.604167, fvco = 2020.000000 MHz

[DEBUG] fdiv = 202, Ndiv = 52.604167, Nint = 52, Nfrac = 633514, fvco = 2020.000000 MHz

[DEBUG] i=6, hi=0, lo=0

[DEBUG] i=5, hi=1, lo=1

[DEBUG] i=4, hi=1, lo=1

[DEBUG] i=3, hi=1, lo=0

[DEBUG] i=2, hi=1, lo=0

[DEBUG] i=1, hi=1, lo=1

[DEBUG] i=0, hi=1, lo=0

[DEBUG] lowest CSW_VCO 71, highest CSW_VCO 77

[DEBUG] i=6, hi=1, lo=1

[DEBUG] i=5, hi=1, lo=1

[DEBUG] i=4, hi=1, lo=1

[DEBUG] i=3, hi=1, lo=1

[DEBUG] i=2, hi=1, lo=1

[DEBUG] i=1, hi=1, lo=1

[DEBUG] i=0, hi=1, lo=1

[DEBUG] lowest CSW_VCO 256, highest CSW_VCO 128

[DEBUG] lowest CSW_VCO 71, highest CSW_VCO 77, CSW_VCO 74

[DEBUG] VCO OK

Actual DATA clock freq 10.000000 MHz

[INFO] SXX[RX] tune 600.000000 MHz (fref=38.400000 MHz) begin

[INFO] VCOFreq: 4800000000.000000, DivLOCH: 2

[INFO] SXX tune 600.000000 MHz (fref=38.400000 MHz) begin

[DEBUG] fdiv = 2, Ndiv = 31.250000, fvco = 1200.000000 MHz

[DEBUG] fdiv = 4, Ndiv = 62.500000, fvco = 2400.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, fvco = 4800.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, fvco = 4800.000000 MHz

[DEBUG] fdiv = 2, Ndiv = 31.250000, fvco = 1200.000000 MHz

[DEBUG] fdiv = 4, Ndiv = 62.500000, fvco = 2400.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, fvco = 4800.000000 MHz

[DEBUG] fdiv = 16, Ndiv = 250.000000, fvco = 9600.000000 MHz

[DEBUG] fdiv = 32, Ndiv = 500.000000, fvco = 19200.000000 MHz

[DEBUG] fdiv = 64, Ndiv = 1000.000000, fvco = 38400.000000 MHz

[DEBUG] fdiv = 2, Ndiv = 31.250000, fvco = 1200.000000 MHz

[DEBUG] fdiv = 4, Ndiv = 62.500000, fvco = 2400.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, fvco = 4800.000000 MHz

[DEBUG] fdiv = 16, Ndiv = 250.000000, fvco = 9600.000000 MHz

[DEBUG] fdiv = 32, Ndiv = 500.000000, fvco = 19200.000000 MHz

[DEBUG] fdiv = 64, Ndiv = 1000.000000, fvco = 38400.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, Nint = 121, Nfrac = 0, DIV_LOCH_SX = 2, fvco = 4800.000000 MHz

[DEBUG] Testing for SEL_VCO = 0

[DEBUG] i=6, hi=0, lo=0

[DEBUG] i=5, hi=0, lo=0

[DEBUG] i=4, hi=0, lo=0

[DEBUG] i=3, hi=0, lo=0

[DEBUG] i=2, hi=0, lo=0

[DEBUG] i=1, hi=0, lo=0

[DEBUG] i=0, hi=0, lo=0

[DEBUG] lowest CSW_VCO 128, highest CSW_VCO 127

[DEBUG] i=6, hi=0, lo=0

[DEBUG] i=5, hi=1, lo=1

[DEBUG] i=4, hi=1, lo=1

[DEBUG] i=3, hi=1, lo=1

[DEBUG] i=2, hi=1, lo=0

[DEBUG] i=1, hi=1, lo=0

[DEBUG] i=0, hi=1, lo=0

[DEBUG] lowest CSW_VCO 193, highest CSW_VCO 199

[DEBUG] lowest CSW_VCO 193, highest CSW_VCO 199, CSW_VCO 196

[DEBUG] VCO OK

[DEBUG] Choosing SEL_VCO = 0

[DEBUG] fdiv = 8, Ndiv = 125.000000, Nint = 121, Nfrac = 0, DIV_LOCH_SX = 2, fvco = 4800.000000 MHz

Actual RX LO freq 600.000000 MHz

[INFO] SXX[TX] tune 600.000000 MHz (fref=38.400000 MHz) begin

[INFO] VCOFreq: 4800000000.000000, DivLOCH: 2

[INFO] SXX tune 600.000000 MHz (fref=38.400000 MHz) begin

[DEBUG] fdiv = 2, Ndiv = 31.250000, fvco = 1200.000000 MHz

[DEBUG] fdiv = 4, Ndiv = 62.500000, fvco = 2400.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, fvco = 4800.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, fvco = 4800.000000 MHz

[DEBUG] fdiv = 2, Ndiv = 31.250000, fvco = 1200.000000 MHz

[DEBUG] fdiv = 4, Ndiv = 62.500000, fvco = 2400.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, fvco = 4800.000000 MHz

[DEBUG] fdiv = 16, Ndiv = 250.000000, fvco = 9600.000000 MHz

[DEBUG] fdiv = 32, Ndiv = 500.000000, fvco = 19200.000000 MHz

[DEBUG] fdiv = 64, Ndiv = 1000.000000, fvco = 38400.000000 MHz

[DEBUG] fdiv = 2, Ndiv = 31.250000, fvco = 1200.000000 MHz

[DEBUG] fdiv = 4, Ndiv = 62.500000, fvco = 2400.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, fvco = 4800.000000 MHz

[DEBUG] fdiv = 16, Ndiv = 250.000000, fvco = 9600.000000 MHz

[DEBUG] fdiv = 32, Ndiv = 500.000000, fvco = 19200.000000 MHz

[DEBUG] fdiv = 64, Ndiv = 1000.000000, fvco = 38400.000000 MHz

[DEBUG] fdiv = 8, Ndiv = 125.000000, Nint = 121, Nfrac = 0, DIV_LOCH_SX = 2, fvco = 4800.000000 MHz

[DEBUG] Testing for SEL_VCO = 0

[DEBUG] VCO select FAIL - too low

[ERROR] VCO select FAIL

Clock tune failure -3

As you can see SXR and SXT settings the same. But SXR tunes fine and SXR not.

System FRef = 38.4MHz, powered from internal LDOs.

My only guess - broken hardware. I don’t have any clues why this is happening. Any help appreciated.

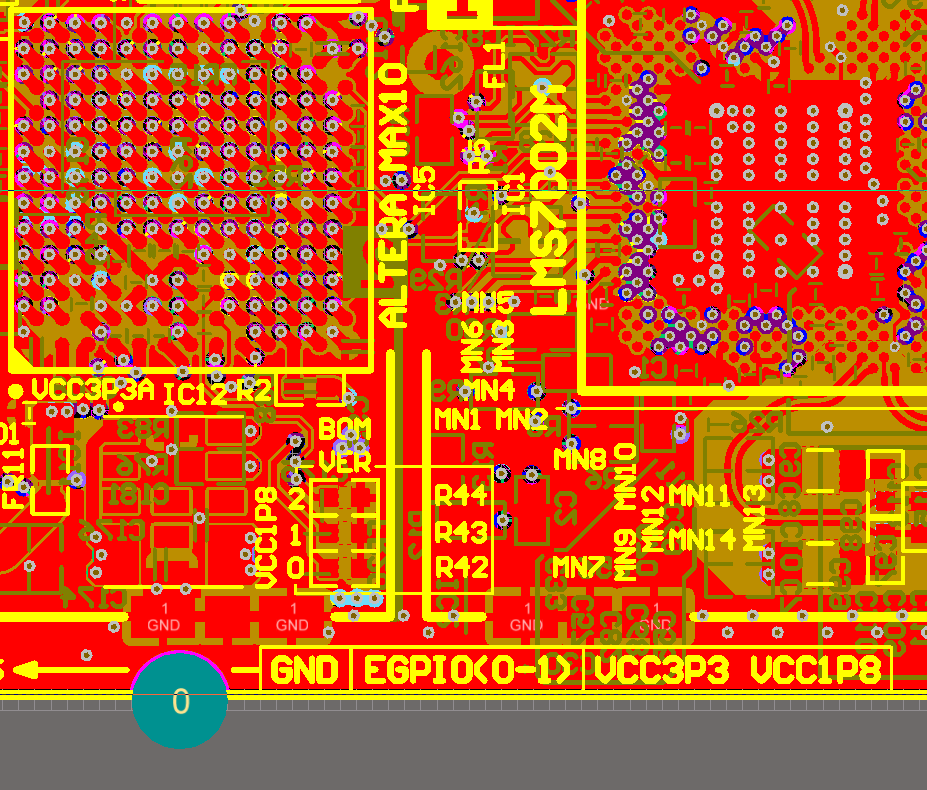

From hardware point of view it is basically LimeSDR-Mini so I don’t know what could be wrong.

From hardware point of view it is basically LimeSDR-Mini so I don’t know what could be wrong.