See:

Board Design and FPGA Gateware Published

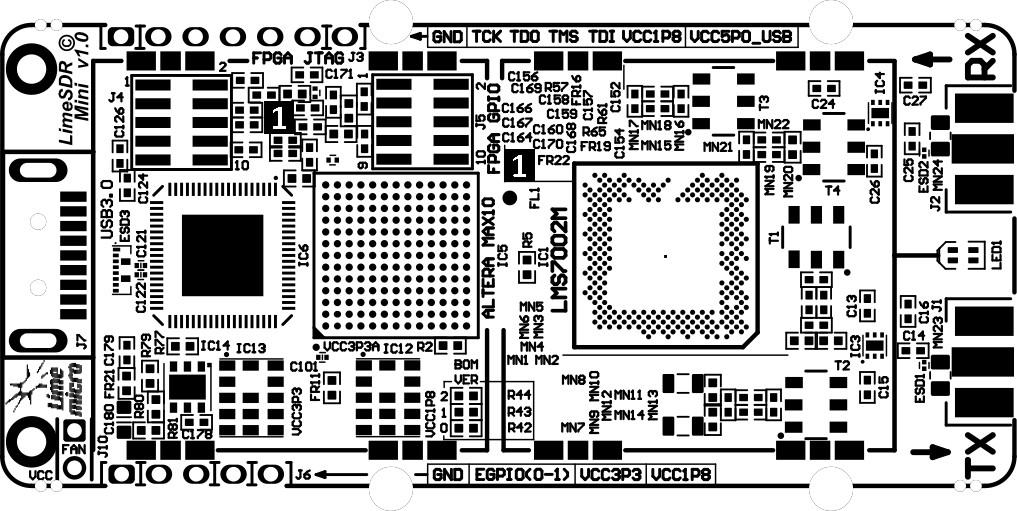

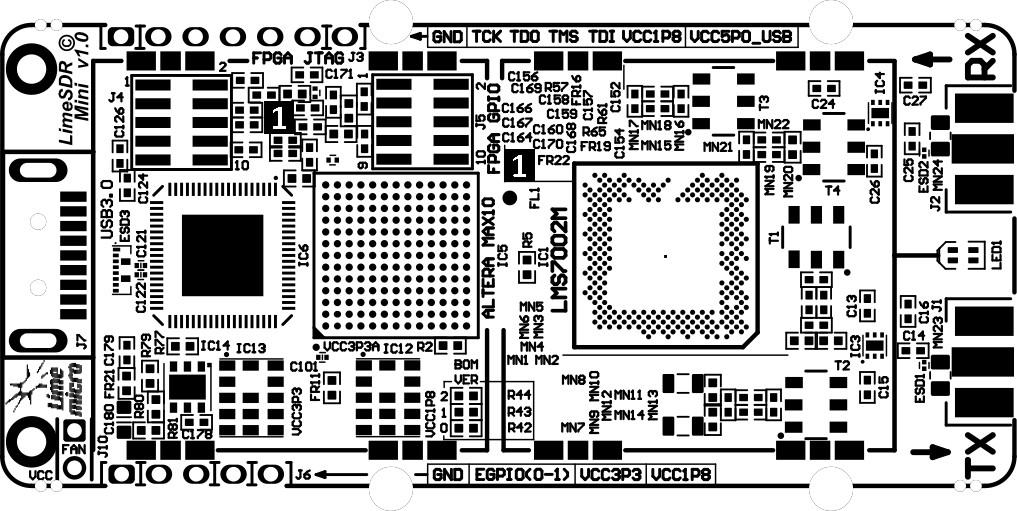

We have published the LimeSDR Mini PCB design database and FPGA gateware RTL sources.

See:

Does anybody know why this device is limited to half the bandwidth of the normal limesdr, is it the FPGA, or FTDI chip that is too weak? Would it be theoretically possible to have bigger bandwidth by reducing the dynamic range (or if signal processing is done on the FPGA)?

My guess is FPGA. Shirley 30MHz is OK? Gives 24MHz usable bandwidth.

It’s 1x1 instead of 2x2 MIMO.

To go to 2x2 would mean more RF connectors, a bigger board and power supply circuitry, additional RF matching etc. As noted a smaller FPGA and uses a simple FTDI device instead of FX3 for USB 3.0 interface too.

Andrew, bit early for questions but I assume that somehow I’ll be able to detect that I’m using the Mini and not the Full LimeSDR?

I do understand, and I am not complaining, I am just a bit curious.

However I tried to ask about the bandwidth (56 MHz Vs 30mhz, not mimo i. e. the amount of independent radio channels/antennas).

Looking at recent commits to Lime Suite it appears to use the device name of LimeSDR-mini, so I would assume so.

Thanks

The LimeSDR Mini board design and FPGA RTL sources have been published:

We have published the LimeSDR Mini PCB design database and FPGA gateware RTL sources.

Hi guy’s,

According to the schematics, the RX/TX in/out stage can be switched (depending on RX/TX frequency)

RX bands:

TX bands:

If I just read the schematics, the limesdr mini will not work for RX on 433Mhz, but as I know there is something similar with the limesdr: Should it work on 433 Mhz in RX AND TX like the limesdr after some tweak ?

Thanks

Hi @caipiblack,

Sorry, there were notes left from old design in schematic. Stay tuned for measurements from first batch.

Hi! Any updates on this?

They have not been received yet. I think we should have them some time next week.

Thank you for the quick response! Regardless there no actual measurements, what were the design goals for each RX input? As @Zack mentioned the notes on the schematic left from the previous design.